Tuesday, February 11. 2014

Z80 Proto Coming Along Nicely

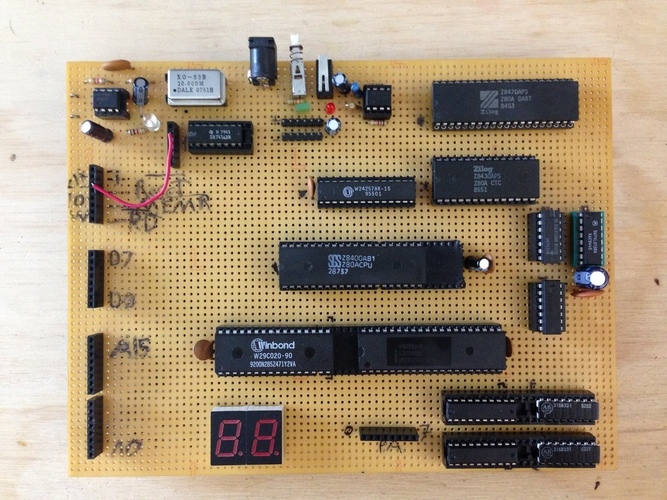

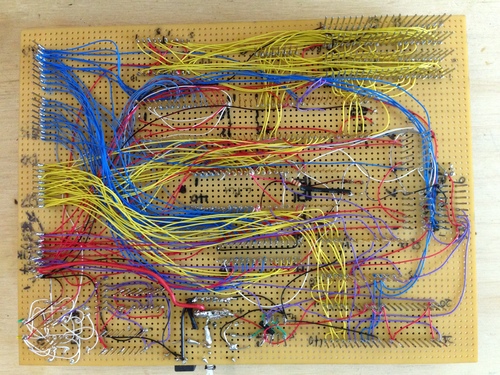

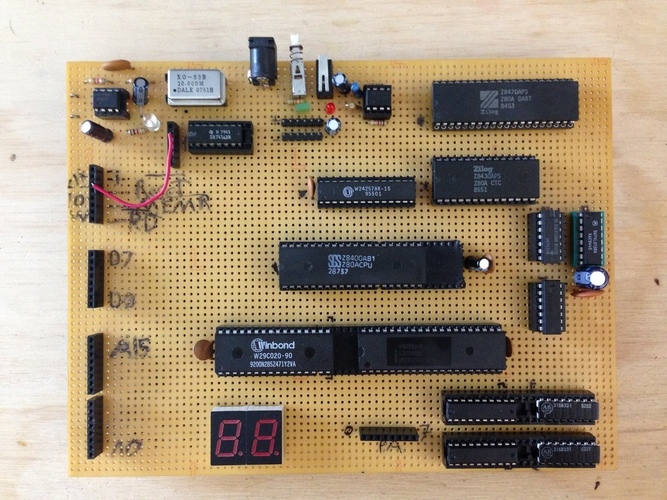

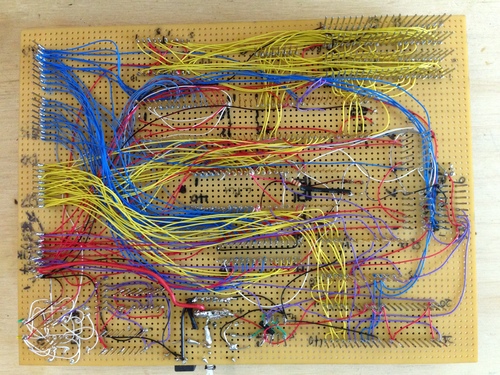

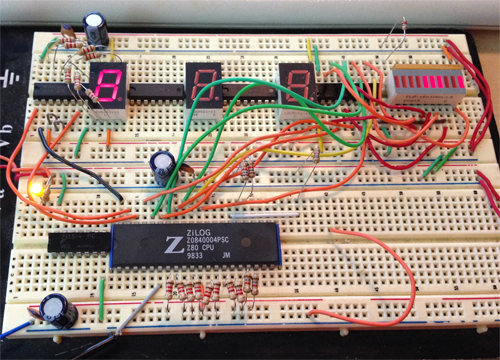

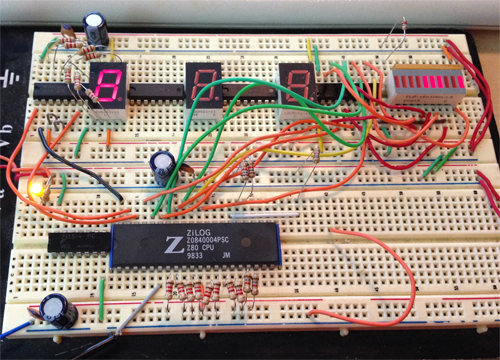

I've rebuilt my previous Z80 computer and have been adding several peripherals of late. I think that ultimatly, after I decide the final design, I'll rebuild the whole thing to look pretty and be better laid out for higher clock speeds, but for now I'm continuing to prototype here.

As it stands, I have the following systems configured:

CPU: Z80A - While I have some later devices with more features and faster clocks on hand, I'm testing base functionality with a run-of-the-mill original.

Flash: W29C020 - Boot ROM. The device is 256 kB, but I'm only using 32k (memory map is split between RAM and ROM). Technically I could enable write functionality to the flash, but haven't done so thus far as I haven't needed it.

SRAM: W24257AK - 32k. Haven't implemented any MMU or paging, but it would be trivial to do so in the future if need be.

Address Decoding and Glue: 74LS138, 74LS32, 74LS04 - Some people use PLAs or GALs to do this in a single device, but I have an attachment 7400 series logic.

General Purpose IO: 8255A - Provides three 8-bit ports per chip. Right now ports A and B are tied to 7-segment displays via 74LS244 octal buffers. Rather than use 7447 7-segment decoders to save 4 bits, I connected the displays directly so that I can display the A-F characters correctly via a map in ROM. This has been quite helpful while writing the BIOS.

Timing: Z8430APS CTC - This guy provides four counter channels with a handy list of prescalers and vectored interrupt features. Right now the BIOS configures channel 0 to send an interrupt every 10ms for polling routines, and channel 1 to provide a compatible baud rate clock to the DART.

Async Serial: Z8470APS DART - Contains a whole slew of serial comm features. Currently the BIOS configures channel A for 9600 8N1 and transmits debugging information through it.

System Clock: 10MHz Osc + 74LS163 Counter - The 4-bit counter provides clocks at 5, 2.5, 1.25, and 0.625 MHz, selectable via pin header. The 555 in the upper-left corner provides a 10kHz clock signal for visual debugging also, but at this point the BIOS is far too long to sit around waiting for it to boot at that clock speed.

Reset Controller: Analog! - At power on, a 1uF capacitor is slowly filled through a 1Mohm resistor to Vcc. When its voltage exceeds that set be a voltage divider (1/2 Vcc here), a comparator (TLC3702) releases the RESET_ assertion. A switch between ground and the capacitor provides another way to trigger a reset.

So far so good! Hopefully I don't jinx myself here, but I haven't made a single wiring mistake yet. I have the logic analyzer sitting here ready, but every time I've added a new chip the unit has just booted right up and worked flawlessly - I can't believe it, given the sheer number of connections.

By the way, I forked the assembler and fixed a few tiny things. Check it out on GitHub: z80asm. Also, I've spent a good bit of time writing emulations of the 8255, CTC, and DART in C as well as fixing the interrupt handling in my fork of z80sim: see my fork here. The file containing the my chip emulations is io.c (a work in progress at the time of writing).

As it stands, I have the following systems configured:

CPU: Z80A - While I have some later devices with more features and faster clocks on hand, I'm testing base functionality with a run-of-the-mill original.

Flash: W29C020 - Boot ROM. The device is 256 kB, but I'm only using 32k (memory map is split between RAM and ROM). Technically I could enable write functionality to the flash, but haven't done so thus far as I haven't needed it.

SRAM: W24257AK - 32k. Haven't implemented any MMU or paging, but it would be trivial to do so in the future if need be.

Address Decoding and Glue: 74LS138, 74LS32, 74LS04 - Some people use PLAs or GALs to do this in a single device, but I have an attachment 7400 series logic.

General Purpose IO: 8255A - Provides three 8-bit ports per chip. Right now ports A and B are tied to 7-segment displays via 74LS244 octal buffers. Rather than use 7447 7-segment decoders to save 4 bits, I connected the displays directly so that I can display the A-F characters correctly via a map in ROM. This has been quite helpful while writing the BIOS.

Timing: Z8430APS CTC - This guy provides four counter channels with a handy list of prescalers and vectored interrupt features. Right now the BIOS configures channel 0 to send an interrupt every 10ms for polling routines, and channel 1 to provide a compatible baud rate clock to the DART.

Async Serial: Z8470APS DART - Contains a whole slew of serial comm features. Currently the BIOS configures channel A for 9600 8N1 and transmits debugging information through it.

System Clock: 10MHz Osc + 74LS163 Counter - The 4-bit counter provides clocks at 5, 2.5, 1.25, and 0.625 MHz, selectable via pin header. The 555 in the upper-left corner provides a 10kHz clock signal for visual debugging also, but at this point the BIOS is far too long to sit around waiting for it to boot at that clock speed.

Reset Controller: Analog! - At power on, a 1uF capacitor is slowly filled through a 1Mohm resistor to Vcc. When its voltage exceeds that set be a voltage divider (1/2 Vcc here), a comparator (TLC3702) releases the RESET_ assertion. A switch between ground and the capacitor provides another way to trigger a reset.

So far so good! Hopefully I don't jinx myself here, but I haven't made a single wiring mistake yet. I have the logic analyzer sitting here ready, but every time I've added a new chip the unit has just booted right up and worked flawlessly - I can't believe it, given the sheer number of connections.

By the way, I forked the assembler and fixed a few tiny things. Check it out on GitHub: z80asm. Also, I've spent a good bit of time writing emulations of the 8255, CTC, and DART in C as well as fixing the interrupt handling in my fork of z80sim: see my fork here. The file containing the my chip emulations is io.c (a work in progress at the time of writing).

Tuesday, January 14. 2014

Z80 Computer and Assembler Adventures

I recently pulled out the Z80 project computer I built several years ago in the hopes of adding some hardware and features to it, but was sad to find that it didn't want to operate in the slightest. A quick connection of the logic analyzer showed that the CPU was not fetching instructions. Hrm. I needed to determine if my delicate, hand-wired little computer was at fault somewhere, or if the CPU itself was upset.

First, I breadboarded the following setup to test the Z80. Since the opcode for the NOP instruction is 0x00, setting the data bus to zeros and providing correct external state causes the chip to simply count up the address bus when clocked. I pulled the data bus to 0s with 1k resistors since the chip is in an undefined state before reset and could attempt to write to the bus - bad news if you're tied to a rail. I then set WAIT_, INT_, NMI_, and BUSREQ_, leaving just a RESET_ and a clock source to add.

I really like the simplicity of Z80: not only can I run the chip with only four pullups and no external components, but it will run with clock speeds all the way down to DC. That means you can single step your computer with a debounced push button as your clock - try that on a modern CPU! For this particular exercise, I rigged a 555 timer to generate a 10hz clock - slow enough to watch the address bus with LEDs.

At the moment of truth, I got... nothing. The chip was tri-stating the address bus and not responding to RESET_. Unfortunately this meant I needed to dig deep into the depths to locate my box of Z80 items that I hadn't seen since college. However, not only did I find the box I was looking for quite quickly, I found a downright awesome pile of parts in there! I recalled that I had 3 extra Z80s and two 82C55's, but in reality I owned 16 Z80s of different vintages and speed grades, a few different types of 82C55, and an awesome pile of Z84 family peripheral controllers. I was very pleased.

Back at my desk, I tested all 17 CPUs (the one that was in my computer, plus the 16 extra ones I had). It turns out that all of my spares are in perfect working condition, and the one in the computer was in fact dead as a door nail. Good to know!

Next, I put a working CPU back in the computer, then wrote, assembled (using z80asm-1.2), and burned the following test program into flash:

LD A,0x80 ; 1000 0000 - tell the 82C55 to set all ports to outputs

OUT (3),A ; 0x03 is the control word address

LD A,1 ; set one bit that we will rotate in the loop

loop: OUT (0),A ; put the word out on port A of the 82C55

NOP

RLCA ; left-rotate reg A

JP loop

Sure enough, it worked great in hardware. Unfortunately, I decided to test the code in an emulator before running the hardware, and ended up spending many hours debugging and rewriting the emulator's memory loading functionality to be properly endian-safe and to autodetect binary blob types, but I'll leave that rant for another time. In any event, this was a great refresher in Z80 architecture and assembly as well as the interworkings of the emulator. Now that my Z80 computer is working, I have no excuse not to add more cool things to the project...

First, I breadboarded the following setup to test the Z80. Since the opcode for the NOP instruction is 0x00, setting the data bus to zeros and providing correct external state causes the chip to simply count up the address bus when clocked. I pulled the data bus to 0s with 1k resistors since the chip is in an undefined state before reset and could attempt to write to the bus - bad news if you're tied to a rail. I then set WAIT_, INT_, NMI_, and BUSREQ_, leaving just a RESET_ and a clock source to add.

I really like the simplicity of Z80: not only can I run the chip with only four pullups and no external components, but it will run with clock speeds all the way down to DC. That means you can single step your computer with a debounced push button as your clock - try that on a modern CPU! For this particular exercise, I rigged a 555 timer to generate a 10hz clock - slow enough to watch the address bus with LEDs.

At the moment of truth, I got... nothing. The chip was tri-stating the address bus and not responding to RESET_. Unfortunately this meant I needed to dig deep into the depths to locate my box of Z80 items that I hadn't seen since college. However, not only did I find the box I was looking for quite quickly, I found a downright awesome pile of parts in there! I recalled that I had 3 extra Z80s and two 82C55's, but in reality I owned 16 Z80s of different vintages and speed grades, a few different types of 82C55, and an awesome pile of Z84 family peripheral controllers. I was very pleased.

Back at my desk, I tested all 17 CPUs (the one that was in my computer, plus the 16 extra ones I had). It turns out that all of my spares are in perfect working condition, and the one in the computer was in fact dead as a door nail. Good to know!

Next, I put a working CPU back in the computer, then wrote, assembled (using z80asm-1.2), and burned the following test program into flash:

LD A,0x80 ; 1000 0000 - tell the 82C55 to set all ports to outputs

OUT (3),A ; 0x03 is the control word address

LD A,1 ; set one bit that we will rotate in the loop

loop: OUT (0),A ; put the word out on port A of the 82C55

NOP

RLCA ; left-rotate reg A

JP loop

Sure enough, it worked great in hardware. Unfortunately, I decided to test the code in an emulator before running the hardware, and ended up spending many hours debugging and rewriting the emulator's memory loading functionality to be properly endian-safe and to autodetect binary blob types, but I'll leave that rant for another time. In any event, this was a great refresher in Z80 architecture and assembly as well as the interworkings of the emulator. Now that my Z80 computer is working, I have no excuse not to add more cool things to the project...

Sunday, April 8. 2007

Current Happenings

Over the past few days I’ve been working on a z80 computer. It’s on breadboards, and includes 2M flash, 32k static ram, and 3 IO ports. It’s quite interesting, and is clearing up lots of my low-level computing knowledge. More on that in a few days.

Today I put much larger motors on the X and Y axis of the mill, having already put a larger motor on the Z axis. The new motors looked great and ran equally as great for about 3 minutes… The new motors pulled much more current than the previous, and I couldn’t remember the ratings on the NPN transistors I used. Turns out its less than what i need.

When I get around to it I’ll make a new driver board with Mosfets rated at 50 amps, should take care of it. The supply I’m using is 5v at 50 amps, so I don’t think any single line can exceed its rating.

The new mill is very slowly coming along… I can’t wait until I can make huge things though.

Today I put much larger motors on the X and Y axis of the mill, having already put a larger motor on the Z axis. The new motors looked great and ran equally as great for about 3 minutes… The new motors pulled much more current than the previous, and I couldn’t remember the ratings on the NPN transistors I used. Turns out its less than what i need.

When I get around to it I’ll make a new driver board with Mosfets rated at 50 amps, should take care of it. The supply I’m using is 5v at 50 amps, so I don’t think any single line can exceed its rating.

The new mill is very slowly coming along… I can’t wait until I can make huge things though.

(Page 1 of 1, totaling 3 entries)

Email me:

jack {@} crepinc.com

Recent Projects:

Analog HF Transmitter

Audi ECU Reverse Engineering

Dual DAC QAM Modulator

FPGA QAM Modulator

Geiger Counter

Gyro-Stabilized DSLR Platform

Hybrid Rocket Engines

Turbocharger Controller

WWVB Rx and Tx

Older Projects:

Balancing Bot

Capacitor Array

CNC Mill

DCIR Renderer

Electric Gokart

Hovercraft

Low Alt. Temp. Model

Shopping Cart Locker

Trebuchet

My Twitter occasionally shows projects I'm working on.

My GitHub has code from a few projects on it.

jack {@} crepinc.com

Recent Projects:

Analog HF Transmitter

Audi ECU Reverse Engineering

Dual DAC QAM Modulator

FPGA QAM Modulator

Geiger Counter

Gyro-Stabilized DSLR Platform

Hybrid Rocket Engines

Turbocharger Controller

WWVB Rx and Tx

Older Projects:

Balancing Bot

Capacitor Array

CNC Mill

DCIR Renderer

Electric Gokart

Hovercraft

Low Alt. Temp. Model

Shopping Cart Locker

Trebuchet

My Twitter occasionally shows projects I'm working on.

My GitHub has code from a few projects on it.